University of London Imperial College of Science, Technology and Medicine Department of Computing

## Customisable and Reconfigurable Platform for Optimising Floating Point Computations

Chun Hok Ho

Submitted in partial fulfilment of the requirements for the degree of Doctor of Philosophy in Computing of the University of London and the Diploma of Imperial College, September, 2009

### Abstract

This research proposes a platform for developing reconfigurable architectures dedicated to floating point computations. The platform involves customisable and reconfigurable architectures with the associated tools and methods for modelling, designing and using the proposed architectures to optimise floating point computations.

Customisability refers to modifying devices to target a specific application domain *before fabrication*. Reconfigurability refers to programming devices to implement different application circuitries in such domain *after fabrication*. A customisable and reconfigurable platform has been delivered, with the following contributions.

(1) Modelling: To model the proposed devices and compare with existing FPGA devices, this thesis proposes a methodology by using existing vendor tools to estimate the area, delay and power consumption of the devices.

(2) Synthesisable Datapath: The proposed architectures capture common patterns appearing in floating point datapaths such as bus-based logic and routing. By exploiting shared configuration bits, we propose a datapath-style coarse-grained reconfigurable fabric. In addition, we adopt synthesisable design flow allowing user customisation.

(3) Floating point FPGA: We propose an FPGA device which consists of island-style fine-grained fabric for general purpose computations and datapath-style coarse-grained fabric for floating point computations. The coarse-grained fabric contains dedicated circuitries for floating point operation and is customisable according to domain-specific requirements.

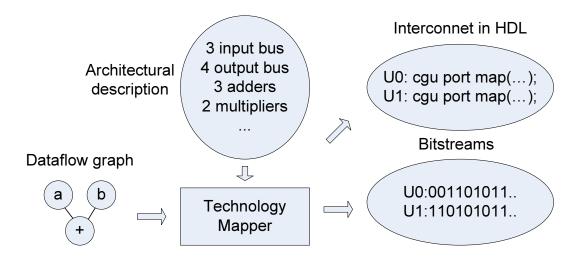

(4) Application design flow: A high level design flow is proposed which can translate a high level description of an application into a reconfigurable implementation. The key component in the high level design flow is a technology mapper which can map a given dataflow graph of an application into reconfigurable devices with different architectural parameters.

Floating point applications have been implemented on an instance of the proposed reconfigurable architecture and promising results have been reported. Application

domains include digital signal processing, scientific applications, and financial applications. Area can be reduced by 25 times and delay can be shortened by 4 times on average, while dynamic energy consumption is reduced by 14 times when compared with a traditional FPGA implementation with comparable technology.

## Acknowledgements

First and foremost, I would like to express my deepest gratitude to my advisor Professor Wayne Luk, for his support, encouragement and trust throughout the years. His insightful comments have improved my papers, presentations, and this thesis tremendously, and his advice has always helped me to make the right decision.

This thesis would not have been possible without the guidance from my secondary thesis advisor Professor Philip Leong. He enlightened me the fascinating reconfigurable computing research and supervised me in both the bachelor and master degree studies. I deeply appreciated his encouragement and suggestions in these years.

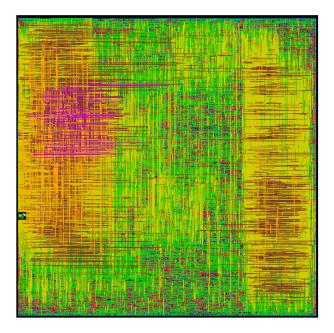

I am indebted to Professor Steven Wilton, for assisting me in designing the architecture of the floating point FPGA. He proposed the synthesisable datapath FPGA architecture (Figure 4.1) described in Chapter 4. His knowledge in System-on-chip development as well as his research attitude inspired me the way to conduct serious scientific research.

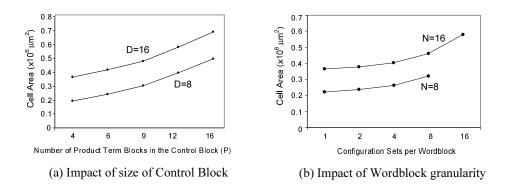

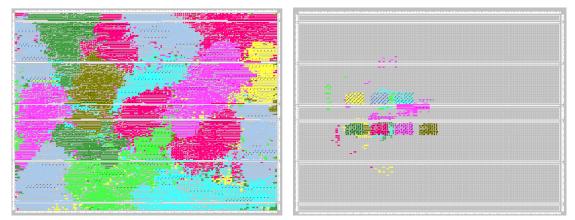

Special thanks are due to Brad Quinton for his collaboration in our synthesisable datapath FPGA architecture study for generating the layout of the datapath FPGA fabric (Figure 4.6).

I would like to express my gratitude to Chi Wai Yu, for his contribution in preparing benchmark circuits used in Chapter 5.

It is a real privilege for me to study in the Custom Computing Group, Department of Computing at Imperial College London. It is one of the largest groups in the world dedicated to reconfigurable computing research. I enjoyed the research experience here and I learnt a lot from my sincere colleagues. Thanks are especially given to Ray Cheung, David Thomas, Kubilay Atasu, Haohuan Fu, Yuet Ming Lam, Kuen Hung Tsoi, Gary Chow, Julien Lamoureux and Markus Koester, for their invaluable supports and countless hours of discussions which help me in preparing this thesis.

During my graduate study, I had the good fortune to receive an internship opportunity and I enjoyed wonderful spring and summer working in the Xilinx Research Labs at San Jose, California. The experience was fruitful and the project gave me the idea of developing high level synthesis tools for floating point FPGA. I would like to express my most sincere thanks to my mentors Prasanna Sundararajan, Jeff Mason and Dave Bennett, for sharing their insights and expertise, which have greatly broadened my knowledge and vision.

My special thanks go to Lucia Lau, Edith Ngai, Dongping Zhang and Olivier Pernet, for their supportive comments and being companionable flatmates who enrich my overseas research experience in the United Kingdom.

The financial support from Overseas Research Students Award Scheme and UK Engineering and Physical Sciences Research Council (grant number EP/D060567/1) is gratefully acknowledged.

## Dedication

To my parents, for raising me to be the person I am today;

and to Angela,

for her continued patience, care, support and love.

## Table of Contents

| Ab  | strac   | t        |                                      | 2  |

|-----|---------|----------|--------------------------------------|----|

| Ac  | know    | ledgen   | ients                                | 4  |

| De  | dicat   | ion      |                                      | 6  |

| Ta  | ble of  | f Conte  | nts                                  | 7  |

| Lis | st of T | ables    |                                      | 11 |

| Lis | st of F | igures   |                                      | 14 |

| Lis | st of F | Publicat | ions                                 | 16 |

| 1   | Intro   | oductio  | n                                    | 17 |

| 2   | Back    | ground   | l and Related Work                   | 23 |

|     | 2.1     | Introd   | uction                               | 23 |

|     | 2.2     | FPGA A   | Architecture                         | 24 |

|     | 2.3     | FPGA I   | Design Tools                         | 27 |

|     | 2.4     | Floatin  | g Point Number System                | 29 |

|     |         | 2.4.1    | Overview                             | 29 |

|     |         | 2.4.2    | Addition and Subtraction             | 30 |

|     |         | 2.4.3    | Multiplication                       | 33 |

|     | 2.5     | FPGA-1   | based Floating Point Units           | 33 |

|     | 2.6     | Floatin  | g Point Applications                 | 40 |

|     | 2.7     | Benchi   | mark Circuits                        | 42 |

|     |         | 2.7.1    | Digital Sine-Cosine Generator (dscg) | 42 |

|     |         | 2.7.2    | Ordinary Differential Equation (ode) | 43 |

|     |         | 2.7.3    | Matrix Multiplication ( <i>mm3</i> ) | 43 |

|     |         | 2.7.4    | FIR Filter ( <i>fir4</i> )           | 44 |

|     |         | 2.7.5    | Butterfly Circuit ( <i>bfly</i> )    | 44 |

|   |      | 2.7.6 Brace, Gątarek and Musiela ( <i>bgm</i> ) | 45 |

|---|------|-------------------------------------------------|----|

|   | 2.8  | Terminology                                     | 46 |

|   | 2.9  | Summary                                         | 47 |

| 3 | Virt | ual Embedded Block                              | 48 |

|   | 3.1  | Introduction                                    | 48 |

|   | 3.2  | Overview                                        | 51 |

|   |      | 3.2.1 VEB Model                                 | 51 |

|   |      | 3.2.2 VEB generation tool                       | 56 |

|   | 3.3  | Vendor Specific Design Flow                     | 58 |

|   |      | 3.3.1 VEB Parameters Estimation                 | 59 |

|   |      | 3.3.2 Integration into Xilinx Tools             | 62 |

|   |      | 3.3.3 Integration into Altera Tools             | 63 |

|   | 3.4  | Results                                         | 64 |

|   |      | 3.4.1 Verification of the VEB Design Flow       | 64 |

|   |      | 3.4.2 Embedded Floating Point Unit              | 66 |

|   |      | 3.4.3 Exploration of Technology Trends          | 68 |

|   | 3.5  | Discussion                                      | 71 |

|   | 3.6  | Summary                                         | 73 |

|   |      |                                                 | -  |

| 4 | ·    | thesisable Datapath FPGA Fabric                 | 76 |

|   | 4.1  | Introduction                                    | 76 |

|   | 4.2  | Overview and Architectural Requirements         | 79 |

|   | 4.3  | Architecture                                    | 81 |

|   | 4.4  | Example Mapping                                 | 84 |

|   | 4.5  | Parameter Optimisation                          | 86 |

|   | 4.6  | Results                                         | 89 |

|   |      | 4.6.1 Benchmark Circuits                        | 90 |

|   |      | 4.6.2 Area Results - Optimised Parameters       | 91 |

|   |      | 4.6.3 Area Results - Derived Parameters         | 95 |

|   |      | 4.6.4 Path Delay Results                           | 97  |

|---|------|----------------------------------------------------|-----|

|   |      | 4.6.5 Delay and Power Results - Derived Parameters | 97  |

|   |      | 4.6.6 Proof-of-Concept Layout                      | 99  |

|   | 4.7  | Comparison to Previous Work                        | 100 |

|   |      | 4.7.1 Alternative Debugging Architectures          | 100 |

|   |      | 4.7.2 Fine-Grained Synthesisable Fabric            | 102 |

|   |      | 4.7.3 Datapath-Oriented FPGAs                      | 103 |

|   |      | 4.7.4 Coarse-Grained Fabrics                       | 103 |

|   | 4.8  | Summary                                            | 104 |

| _ |      |                                                    | 10- |

| 5 | Floa | ting Point FPGA: Architecture and Modelling        | 107 |

|   | 5.1  | Introduction                                       | 107 |

|   | 5.2  | FPFPGA Architecture                                | 109 |

|   |      | 5.2.1 Requirements                                 | 109 |

|   |      | 5.2.2 Architecture                                 | 111 |

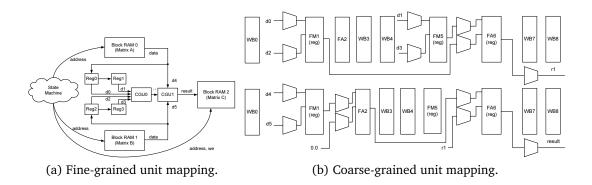

|   | 5.3  | Example Mapping                                    | 115 |

|   | 5.4  | Modelling                                          | 116 |

|   |      | 5.4.1 Overview                                     | 116 |

|   |      | 5.4.2 Power Modelling                              | 118 |

|   | 5.5  | Results                                            | 120 |

|   | 5.6  | Comparison with Previous Work                      | 126 |

|   | 5.7  | Summary                                            | 128 |

| c |      |                                                    | 101 |

| 6 |      | Tools for Floating Point FPGA                      | 131 |

|   | 6.1  |                                                    | 131 |

|   | 6.2  | Requirements                                       | 134 |

|   | 6.3  | Technology mapper                                  | 136 |

|   |      | 6.3.1 Overview                                     | 136 |

|   |      | 6.3.2 Algorithm                                    | 139 |

|   |      | 6.3.3 Bitstream Generator                          | 146 |

| Bil | oliogi | raphy 10                  | 63 |

|-----|--------|---------------------------|----|

|     | 7.2    | Future Work               | 59 |

|     |        | Summary of Achievements 1 |    |

| 7   | Con    | clusion 1                 | 56 |

|     | 6.6    | Summary                   | 55 |

|     | 6.5    | Results                   | 54 |

|     |        | 6.4.2 The fly compiler    | 52 |

|     |        | 6.4.1 Trident             | 50 |

|     | 6.4    | Integration               | 49 |

|     |        | 6.3.4 Example             | 48 |

## List of Tables

| 2.1 | FPGA-based floating point operators implementations                      | 34 |

|-----|--------------------------------------------------------------------------|----|

| 2.2 | Number of tests generated by <i>TestFloat-2a</i>                         | 40 |

| 2.3 | FPGA implementation results for double precision floating point oper-    |    |

|     | ators                                                                    | 40 |

| 3.1 | Delay parameters for Virtex II-6 devices.                                | 60 |

| 3.2 | Delay parameters for Stratix-6 devices.                                  | 61 |

| 3.3 | Estimates of logic cell area including configuration bit, buffer and in- |    |

|     | terconnect overheads. There is no public information about the die       |    |

|     | area of Stratix device so we assume that it has the same normalised LC   |    |

|     | area as the one in Virtex II 1000 device.                                | 61 |

| 3.4 | Summary of resource utilisation and critical path delay for embed-       |    |

|     | ded multiplier (MULT18X18S) and VEB implementations on an Xilinx         |    |

|     | XC2V6000-FF1152-6 device. An asterisk (*) indicates that retiming is     |    |

|     | enabled during synthesis                                                 | 65 |

| 3.5 | Summary of resource utilisation and critical path delay for 18x18 em-    |    |

|     | bedded multiplier in DSP block and VEB implementations on an Altera      |    |

|     | EP1S80F1508C6 device. An asterisk (*) indicates that retiming is en-     |    |

|     | abled during synthesis.                                                  | 65 |

| 3.6 | Breakdown of critical path delay for embedded multiplier and VEB im-     |    |

|     | plementations on a XC2V6000 device. bg $m^*$ indicates that retiming is  |    |

|     | enabled during synthesis.                                                | 66 |

| 3.7 | FPGA implementation results for floating point benchmark applica-        |    |

|     | tions on a Xilinx XC2V6000-6-FF1152 device. The VEB size is given        |    |

|     | as the FPU area (in equivalent LC resources) plus the LC resources       |    |

|     | needed to implement the rest of the circuit. The second column (EMs)     |    |

|     | indicates number of MULT18X18S instantiated.                             | 67 |

| 3.8  | FPGA implementation results for floating point benchmark applica-      |     |

|------|------------------------------------------------------------------------|-----|

|      | tions on an Altera EP1S80F1508C6 device. The VEB size is given as the  |     |

|      | FPU area (in equivalent LC resources) plus the LC resources needed to  |     |

|      | implement the rest of the circuit. The second column (EMs) indicates   |     |

|      | number of 9x9 multipliers instantiated.                                | 67  |

| 3.9  | Comparison of VEB and VPR                                              | 74  |

| 4.1  | Architectural parameters.                                              | 84  |

| 4.2  | Meaning of mask bits in the example                                    | 85  |

| 4.3  | Area breakdown.                                                        | 88  |

| 4.4  | Parameters used for each benchmark circuit.                            | 92  |

| 4.5  | Area results when the fabric is optimised for each benchmark circuit   | 92  |

| 4.6  | Parameters used for each benchmark circuit when low-level parame-      |     |

|      | ters are computed.                                                     | 95  |

| 4.7  | Area results when low-level parameters are computed                    | 95  |

| 4.8  | Delay estimates of paths within fabric                                 | 97  |

| 4.9  | Datapath delay and power estimates for configured fabric               | 99  |

| 4.10 | Comparison of coarse-grained reconfigurable fabric.                    | 105 |

| 5.1  | Parameters for the coarse-grained unit                                 | 113 |

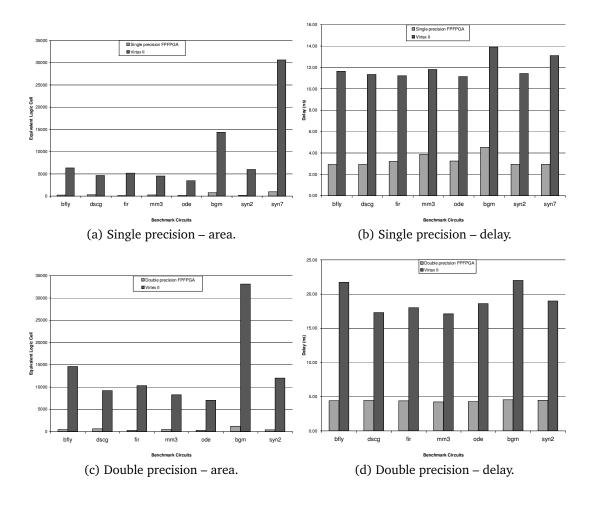

| 5.2  | Benchmark circuits                                                     | 120 |

| 5.3  | Normalisation on the area of the coarse-grained units against a Virtex |     |

|      | II LC. SP and DP stand for single precision and double precision re-   |     |

|      | spectively. For the values shown in the second column (Area), 15%      |     |

|      | overheads have already been applied on the coarse-grained units        | 122 |

| 5.4  | FPFPGA implementation results. Values in the brackets indicate the     |     |

|      | percentages of logic cell used in corresponding FPGA device. CGU       |     |

|      | stands for coarse-grained unit and FGU stands for fine-grained unit.   | 129 |

| 5.5 | Power estimations. *Circuit <i>syn7</i> cannot fit in a XC2V3000-6 FPGA |     |

|-----|-------------------------------------------------------------------------|-----|

|     | so the power number of FPGA implementation is obtained from a           |     |

|     | XC2V8000-5 FPGA                                                         | 130 |

| 5.6 | Comparison of floating point reconfigurable fabric. Area reduction and  |     |

|     | speedup are compared to an FPGA device with embedded multiplier.        | 130 |

| 5.7 | Comparison to previous embedded FPU model for double precision          |     |

|     | floating point benchmarks.                                              | 130 |

|     |                                                                         |     |

| 6.1 | Performance of the technology mapper. Most circuits require minimum     |     |

|     | number of coarse-grained unit (CGU).                                    | 154 |

# List of Figures

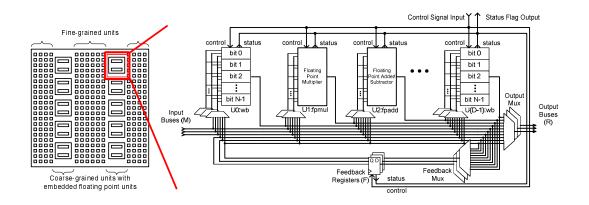

| 1.1 | Floating Point FPGA                                                 | 20  |

|-----|---------------------------------------------------------------------|-----|

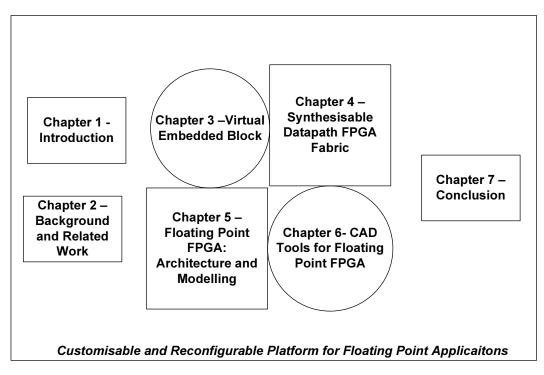

| 1.2 | Relationship diagram of each chapter                                | 21  |

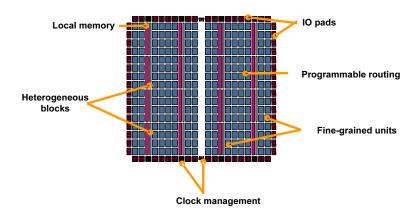

| 2.1 | Standard island-style FPGA architecture                             | 24  |

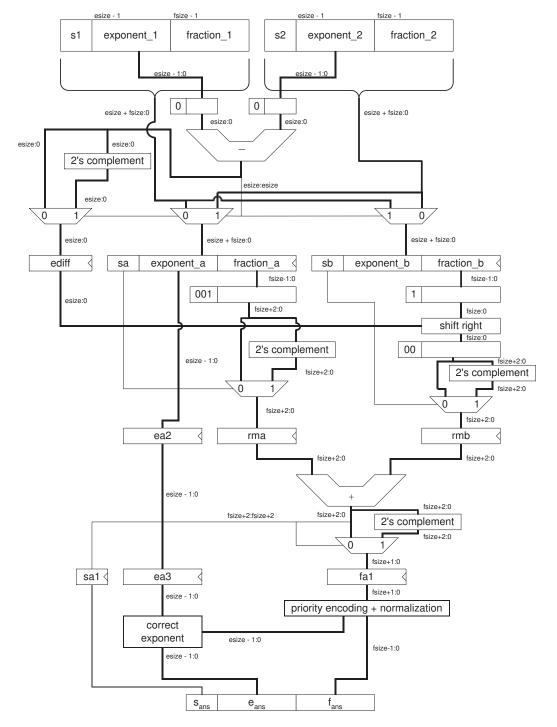

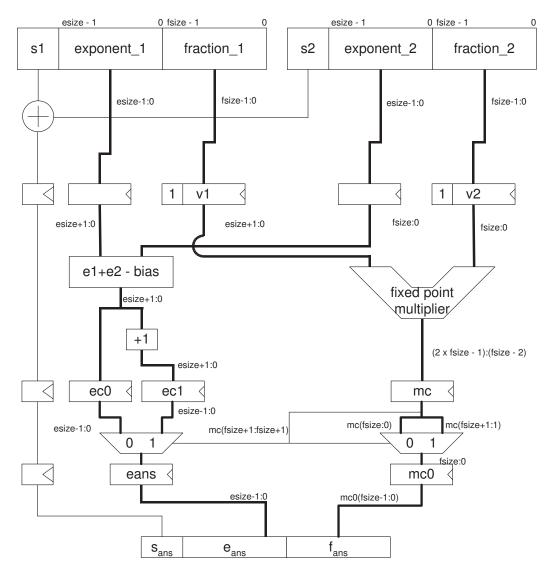

| 2.2 | Datapath of floating point adder.                                   | 36  |

| 2.3 | Datapath of floating point multiplier                               | 37  |

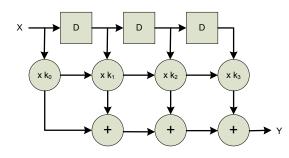

| 2.4 | Four-tap FIR filter.                                                | 44  |

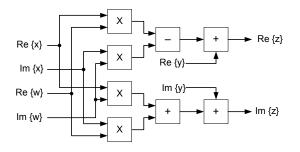

| 2.5 | One butterfly stage in FFT.                                         | 45  |

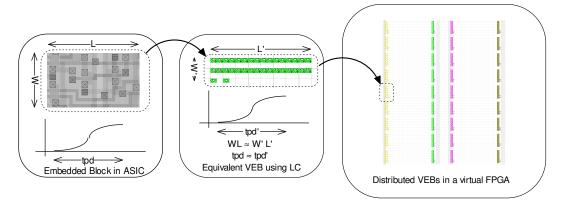

| 3.1 | Modelling embedded elements in FPGAs using Virtual Embedded Blocks. | 52  |

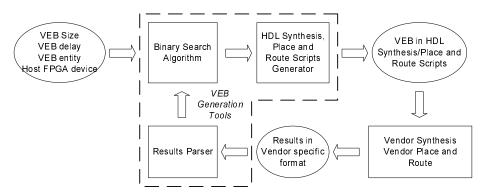

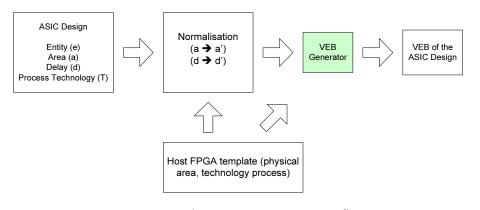

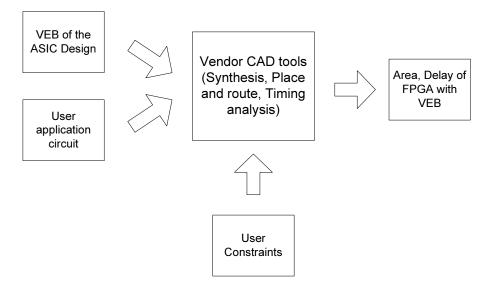

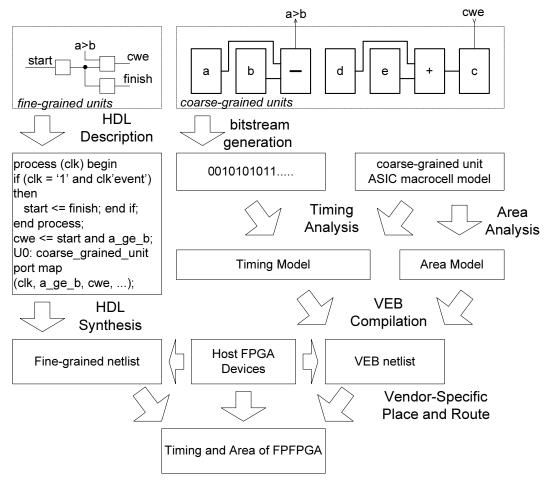

| 3.2 | The block diagram of the VEB design flow                            | 56  |

| 3.3 | Phase 1 – VEB creation flow.                                        | 58  |

| 3.4 | Phase 2 – VEB integration flow.                                     | 58  |

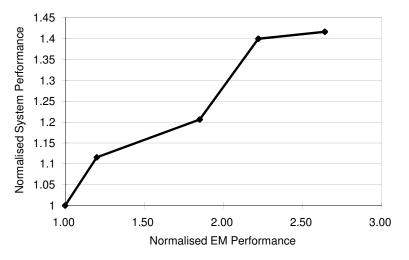

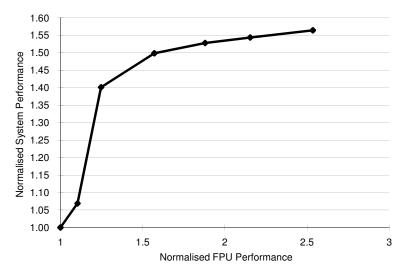

| 3.5 | Performance of fixed-point bgm benchmark with different VEBs, with  |     |

|     | retiming.                                                           | 70  |

| 3.6 | Performance of floating-point bfly benchmark with different FPU de- |     |

|     | lays, with retiming.                                                | 70  |

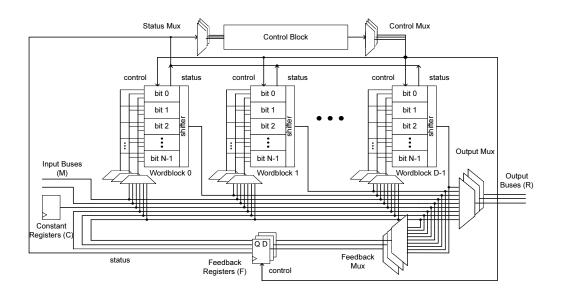

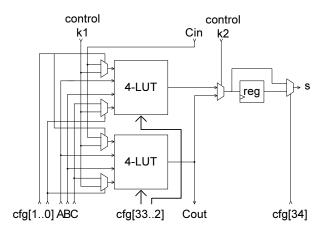

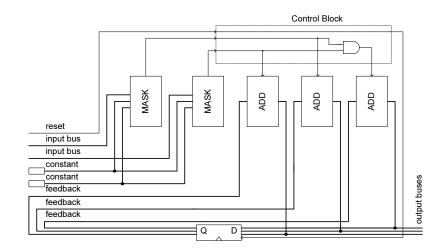

| 4.1 | Fabric architecture (configuration elements not shown)              | 81  |

| 4.2 | Bitblock (status flags not shown)                                   | 83  |

| 4.3 | Example mapping                                                     | 85  |

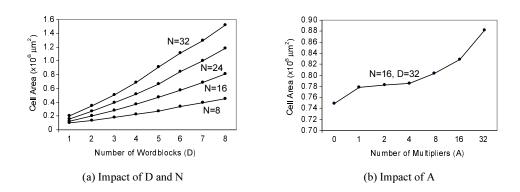

| 4.4 | Parameter sweeps, where M=3, R=2, F=3, C=2, A=4, P=4 unless         |     |

|     | otherwise specified                                                 | 87  |

| 4.5 | Parameter sweeps, where M=3, R=2, F=3, C=2, A=4, P=4 unless         |     |

|     | otherwise specified                                                 | 87  |

| 4.6 | Proof-of-concept layout.                                            | 100 |

| 5.1 | Architecture of the FPFPGA.                                         | 113 |

| 5.2 | Architecture of the coarse-grained unit.                            | 114 |

| 5.3 | Example mapping for matrix multiplication.                          |     |

| 5.4 | Modelling flow overview.                                            | 117 |

|-----|---------------------------------------------------------------------|-----|

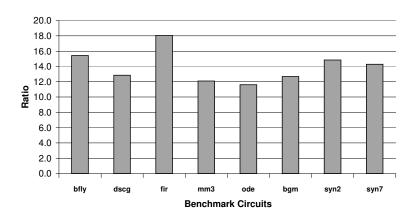

| 5.5 | Comparisons of FPFPGA and Xilinx Virtex II FPGA device              | 125 |

| 5.6 | Floorplan of the single precision bgm circuit on Virtex II FPGA and |     |

|     | FPFPGA. Area is significantly reduced by introducing coarse-grained |     |

|     | units                                                               | 125 |

| 5.7 | Dynamic energy consumption ratio of single precision FPFPGA         | 127 |

| 6.1 | Logic flow of the technology mapper.                                | 136 |

| 6.2 | Sample dataflow graph and its representation                        | 138 |

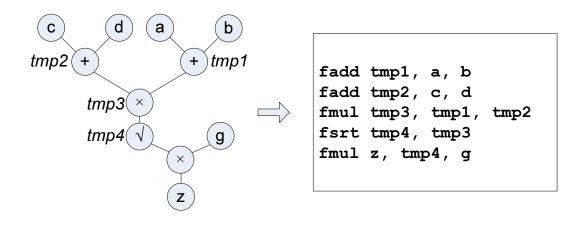

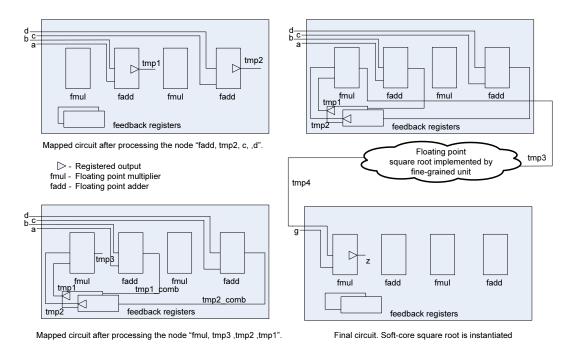

| 6.3 | Mapping of equation $z = \sqrt{a + b \times c + d} \times g$        | 148 |

|     |                                                                     |     |

## **List of Publications**

- C.H. Ho, C.W. Yu, P.H.W. Leong, W. Luk and S.J.E. Wilton, "Floating Point FPGA: Architecture and Modelling", to appear in *IEEE Transactions on Very Large Scale Integration Systems*.

- S.J.E. Wilton, C.H. Ho, B. Quinton, P.H.W. Leong and W. Luk, "A Synthesizable Datapath-Oriented Embedded FPGA Fabric for Silicon Debug Applications", in ACM Transaction of Reconfigurable Technology and Systems, 1(1):7:1–7:25, March 2008.

- C.H. Ho, P.H.W. Leong, W. Luk and S.J.E. Wilton, "Rapid Estimation of Power Consumption for Hybrid FPGAs", in *Proceedings of Field Programmable Logic*, pp. 227–232, 2008. Stamatis Vassiliadis outstanding paper award.

- C.H. Ho, C.W. Yu, P.H.W. Leong, W. Luk and S.J.E. Wilton, "Domain-Specific FPGA: Architecture and Floating Point Applications", in *Proceedings of Field Programmable Logic*, pp. 196–201, 2007. Stamatis Vassiliadis outstanding paper award.

- S.J.E. Wilton, C.H. Ho, P.H.W. Leong, W. Luk and B. Quinton, "A Synthesizable Datapath-Oriented Embedded FPGA Fabric", in *Proceedings of Fifteenth ACM/SIGDA International Symposium on FPGAs*, pp. 33–41, 2007.

- C.H. Ho, P.H.W. Leong, W. Luk, S.J.E. Wilton, S. Lopez-Buedo, "Virtual Embedded Blocks: A Methodology for Evaluating Embedded Elements in FPGAs", in *Proceedings of Field-Programmable Custom Computing Machines*, pp. 35–44, 2006.

## Chapter 1

# Introduction

Improvements in floating point performance have led to major advances in applications as diverse as weather forecasting, problem modelling, financial engineering, molecular dynamics and drug discovery. Although supercomputers based on microprocessor clusters are commonly used for these applications, it appears that their efficiency in terms of sustained performance and power consumption can be significantly improved through increased fined-grained parallelism and better memory utilisation. A good example of a processor optimised for power consumption and performance is the one used in IBM Roadrunner machine [Craw 08], which is currently one of the fastest supercomputers [Dong 08]. Yet we note that its floating point unit (FPU), which contributes more than 95% computation time in benchmark programs like LIN-PACK [Dong 03] as well as many other floating point applications like Monte Carlo simulation and N-body problem, constitutes only 10% of the total roadrunner computation chip (Cell Broadband Engine) area [Flac 05]. The other 90% serves to provide the FPUs with data and perform tasks such as caching, instruction fetching, memory decoding, speculative execution, register files, etc. In addition, the high power consumption of general-purpose processors prohibits the use of floating point arithmetic in low cost embedded systems. We believe that using spatially-parallel hardware oriented techniques with a cluster of FPUs often has advantages in terms of performance, power consumption and area over the traditional general-purpose processor approach.

It is possible to build a dedicated circuit for a specific floating point application using application specific integrated circuit (ASIC) technology, which offers the potential to achieve the highest performance with the least power consumption and area. However, the associated fabrication cost and design time preclude their use in low to medium volume applications, and ASIC designs are not flexible since the circuits cannot be changed once they are fabricated. Another way of implementing floating point applications is to use field programmable gate array (FPGA) technology. An FPGA contains an array of logic gates and storage elements, in which the functionality and interconnection can be configured by downloading a bitstream into its configuration memory. Given a flexible FPGA architecture, a tailor-made datapath and an FPU cluster, a floating point application is likely to have faster execution speed and lower power consumption than general-purpose processors. FPGA technology has been successfully applied to accelerate a large number of diverse applications including signal processing, communications, networking and robotics. The application of FPGA technology to computational problems is also known as reconfigurable computing.

In recent years there has been a significant increase in the size of FPGAs. Current FPGA technology allows arbitrary precision floating point arithmetic while retaining hardware speed. Recent work on dot product, matrix-vector and matrix multiplication [Unde 04] indicates that FPGAs will soon be able to significantly outperform modern microprocessors because of advantages in memory bandwidth and in floating point performance. Another study [Dou 05] shows that an FPGA-based FPU implementation can achieve 15.6 GFLOPS (billion floating point operations per second) with 1.6 MB local memory and a 400 MB/s external memory bandwidth. Our previous research [Ho 02a] indicated that using different arbitrary size of floating point operation in a single design can reduce the circuit area while the accuracy can remain the same. In addition, another work [Zhan 05] shows that an FPGA-based implementation of BGM financial model running at 50MHz is over 25 times faster than software

computations on a 1.5 GHz Intel Pentium 4 machine. However, as the current FPGA architecture only embeds blocks for fixed point operations such as fast carry-chains and block multipliers, it is expected that the computation speed can be made even faster and the power consumption can be lower if more primitive blocks optimised for floating point operations are embedded in FPGAs.

Having better floating point performance in terms of speed, area and power consumption is beneficial to several domains of applications. For example, in Monte Carlo simulation models, increasing performance of floating point operations will allow more paths to be simulated, and therefore the result will be more accurate and faster to converge. Financial applications which require real-time response can meet stringent timing requirement with less hardware, and therefore reduce the associated cost. Graphics applications can process more transformations to produce more realistic effects. Reduction in power consumption of floating point operations allows longer battery life for embedded systems, significantly improving their effectiveness.

The research proposes a *platform* for developing and using novel reconfigurable architectures which improve the execution speed of floating point computations while retaining their programmability. In particular, we propose a standard island-style FPGA architecture coupled with novel reconfigurable heterogeneous fabric to facilitate the *reconfigurable* aspect of this platform. By adopting FPGA architectures, one can implement different applications and datapaths on FPGA devices *after fabrication*.

The platform consists of tools allowing *customisation* of reconfigurable devices *before fabrication*. Using standard macrocell design flow, one can customise their own reconfigurable device by specifying architecture parameters of the heterogeneous fabric. Such customisation enables further optimisations on domain-specific applications. Moreover, the platform consists of high level synthesis tools allowing users to implement floating point applications into the novel FPGA device using higher abstraction of description. The high level synthesis tools also assist the design and development of heterogeneous fabric.

Figure 1.1: Floating Point FPGA.

We propose a hypothesis that certain specific reconfigurable architecture can accelerate floating point computations with much less silicon area and energy. To verify this hypothesis, we evaluate instances of reconfigurable architecture based on a set of benchmark circuits. Figure 1.1 shows an instance of a typical customisation of such reconfigurable architecture. More details are discussed in Chapter 5.

To summarise, a *customisable* and *reconfigurable platform* for optimising floating point computations has been developed, with the following contributions.

- (A) Modelling: To model the proposed devices and compare with existing FPGA devices, this thesis proposes a modelling methodology by using existing vendor tool to estimate the area, delay and power consumption of the devices.

- (B) Synthesisable Datapath: The proposed architectures capture the common pattern appearing in floating point datapaths such as bus-based logic and routing. By exploiting shared configuration bits, we propose a datapath-style coarse-grained reconfigurable fabric. In addition, we adopt synthesisable design flow allowing user customisation.

- (C) Floating point FPGA: We propose an FPGA device which consists of island-style fine-grained fabric for general purpose computations and datapath-style coarsegrained fabric for floating point computations. The coarse-grained fabric contains dedicated circuitries for floating point operation and is customisable ac-

cording to domain-specific requirements.

(D) Application design flow: A high level design flow is proposed which can translate a high level description of an application into a reconfigurable implementation. The key component in the high level design flow is a technology mapper which can map a given dataflow graph of an application into reconfigurable devices with different architectural parameters.

Figure 1.2: Relationship diagram of each chapter.

Figure 1.2 provides a relationship diagram of each chapter in the thesis. Each block corresponds to a chapter in the thesis. Circular blocks indicate contributions related to software aspects while square blocks indicate contributions related to hardware aspects. Rectangular blocks refer to auxiliary materials.

**Chapter 2** offers a comprehensive literature review of related work. The chapter introduces island-style FPGA architecture, the associated CAD tools to model and to program FPGA devices, the floating point number system, the FPGA-based implementations of floating point operators and benchmarks circuits employed to evaluate floating point FPGA architectures. The circuits can be as small as a simple dot-vector product or as large as interest rate model derivatives.

**Chapter 3** demonstrates a methodology to model a commercial FPGA with arbitrary embedded blocks. This chapter corresponds to Contribution A and it addresses one of the important challenges in this thesis – how to conduct a meaningful comparison with real FPGA.

**Chapter 4** proposes a customisable and reconfigurable heterogeneous architecture and a synthesisable design flow which can model this architecture. The parameterised architecture allows us to search for a near-optimum floating point FPGA design. This chapter corresponds to Contribution B and it is an initial attempt to approach new architecture for floating point computation.

**Chapter 5** presents a novel floating point FPGA architecture by extending the heterogeneous architecture discussed in Chapter 4 and employing the FPGA modelling methodology used in Chapter 3. This chapter corresponds to Contribution C and we evaluate the performance of proposed FPGA architecture in area, speed, and dynamic power consumption.

**Chapter 6** describes a high level synthesis flow to support the proposed reconfigurable architecture. The chapter demonstrates an architecture-aware technology mapper which can be integrated into existing hardware compiler to produce circuits implemented on the proposed reconfigurable device. This chapter corresponds to Contribution D.

Conclusion of the thesis and suggestions for future work are made in Chapter 7.

## Chapter 2

# **Background and Related Work**

#### 2.1 Introduction

This chapter presents an introduction to the concepts and terminology relevant to the thesis. It covers both development and usage of reconfigurable devices. The chapter begins with a brief overview of standard FPGA architecture. The concepts of fine-grained units and heterogeneous blocks are explained with published work as examples. The development of current floating point units on commercial FPGA devices is described and the operations involved in floating point circuitry are illustrated. This chapter reports a set of FPGA-based floating point operators and they are used as baseline to evaluate our work. We also show that these operators are compliant with the IEEE 754 standard. It is crucial to maintain the integrity of the thesis such that a justified comparison is allowed. Examples which demand intensive floating point operations are presented to demonstrate the importance of high speed floating point arithmetic. It is followed by an introduction to a set of benchmark circuits which are used iteratively in the thesis. The benchmark circuits include small kernels which capture common operations used in digital signal processing and linear algebra computations. The selected kernels require intensive floating point operation. The chapter concludes number of design flows to model reconfigurable architecture. Finally, a list of termi-

Figure 2.1: Standard island-style FPGA architecture.

nology is given to summarise some acronyms and technical terms uses iteratively in the thesis.

#### 2.2 FPGA Architecture

Figure 2.1 shows the block diagram of a standard island-style FPGA structure. An FPGA is made up of reconfigurable fabric. The fabric itself consists of arrays of finegrained units and heterogeneous blocks. A fine-grained unit usually implements a single function and has a single bit output. The most common fine-grained unit is a K-input lookup table (LUT), where K typically ranges from 4 to 6. The LUT can implement any Boolean equation of K-inputs. This type of fabric is called a LUT-based fabric. Several LUT-based cells can be joined in a hardwired manner to make a cluster. This results in little loss in flexibility but can reduce area and routing resources within the fabric [Ahme 04].

Fine-grained units can also be implemented using a product-term block consisting of an AND plane and an OR plane. The area of a product-term block is usually larger than that of a LUT-based fabric, as it usually has larger fan-in along with small amounts of routing resources to connect the planes. We consider the product-term unit to be a fine-grained unit, because it usually has a small number of output bits. Product-term blocks appear in system-on-chip [Yan 06] as well as commercial CPLD devices.

While a fine-grained unit is flexible and can usually implement any Boolean function, the area, delay and power overhead of an array of fine-grained units that implement a given function are often significantly larger than an appropriate heterogeneous block. Commercial FPGAs, which employ fine-grained fabric as the major component, include special features in the fabric dedicated to operations which are common in digital design. A notable example is the dedicated carry-chain on both Xilinx and Altera devices. The reason for adding such feature is obvious - integer addition and subtraction are common operations for all digital circuits. Multiplexers are another example, as they are inferred frequently in a digital design.

A heterogeneous block is usually less flexible and is typically much larger than a finegrained one, but is often more efficient for implementing specific functions. The heterogeneous block is usually programmable to some degree, combining several functions such as those in an arithmetic logic unit (ALU). Outputs are often bus-based. They can be parameterised in terms of features such as bus-width and functionality. As an example, the ADRES architecture [Mei 03] assumes that the wordlength and the functionality of a heterogeneous block is the same as the targeted processor.

Heterogeneous functional blocks are found on commercial FPGA devices. For example, a Virtex II device has embedded fixed-function 18-bit multipliers and a Xilinx Virtex 4 device has embedded DSP units with 18-bit multipliers and 48-bit accumulators. The flexibility of these blocks is limited and it is less common to build a digital system solely using these blocks. When the blocks are not used, they consume die area and may contribute to increased delay without adding to functionality.

Numerous research projects on FPGA architecture to support domain-specific applications have been conducted. Leijten-Nowak and van Meerbergen [Leij 03] proposed mixed-level granularity logic blocks and compared their benefits with a standard island-style FPGA using the Versatile Place and Route tool (VPR) [Betz 99]. Ye, Rose and Lewis [Ye 03] studied the effects of coarse grained logic cells and routing resources for datapath circuits, also using VPR.

Kuon [Kuon 07] has reported the effectiveness of embedded elements in current FPGA devices by comparing with the equivalent ASIC circuit under 90*nm* technology process. Akan'Ova et al. [Aken 05] has demonstrated a standard-cell-based FPGA with improving performance using a structural design and layout approach. Compton and Hauck [Comp 04] have suggested a flexibility measurement on domain-specific reconfigurable architecture. Beck revised VPR to explore the effects of introducing hard macros [Beck 04]. A more recent VPR tool [Luu 09] supports single-driver routing configuration, and heterogeneous blocks, and provides optimised electrical models.

Several previous studies have considered datapath-oriented FPGAs [Cher 96, Hauc 04, Leij 03, Ye 06, Ye 03]. In these architectures, configuration bits are shared among multiple lookup-tables and multiple routing switches.

Coarse-grained architectures, in which lookup-tables are replaced by ALUs, have also been described in [Cron 99, Gold 00, Mars 99, Sing 00, Ebel 96]. Of these, the RaPiD architecture [Ebel 96] is specifically designed for use in an SoC. RaPiD contains a linear array of dedicated functional units connected using dedicated buses. Control logic is implemented using a separate module that provides control signals to the functional units.

RaPiD is intended to support fairly large applications such as image and signal processing, and may be best implemented as a hard programmable logic core. It would be possible to "scale down" RaPiD and use it as a synthesisable core. However, like the datapath FPGAs described in the previous section, the unconfigured RaPiD fabric contains combinational loops. Our architecture eliminates these using a directional routing network.

While many studies can satisfy certain domain-specific applications, they fail to recognise the applications which demand intensive floating point computations. Our project aims at inventing methodology and architecture to produce an FPGA optimised for floating point computations.

There are a few research projects dedicated to FPGA architecture for floating point computations. Beauchamp et al. augmented VPR to assess the impact of embedding floating-point units in FPGAs [Beau 08]. The study of embedded heterogeneous blocks for the acceleration of floating point computations has been reported by Roseler and Nelson [Roes 02]. Both studies conclude that employing heterogeneous blocks in designing FPU on FPGAs achieves area saving and increased clock rate over a fine-grained approach.

However, the work in [Roes 02] does not take account of the architectural modification of the FPGA device and solely adopts existing heterogeneous blocks in FPGA device to design floating point units. Our research considers any potential embedded elements, including embedded floating point unit, or embedded floating point operators in the design of fabric. It is described in Chapter 5.

While [Beau 08] evaluate the results by employing a modified VPR flow, where floating point unit model is added to the VPR design flow, their work inherits the limitation given by VPR. For instance, as direct comparison to commercial FPGA device cannot be made, the results may not reveal the actual situation. In addition, since their work does not consider any routing resource optimisation as well as bus-based logic optimisation, their reported results may tend to be too conservative. This project proposes a model which is comparable to existing FPGA device and that could produce more realistic results. This methodology is discussed in Chapter 3.

#### 2.3 FPGA Design Tools

Different strategies have been proposed to model FPGA architectures. The VPR computer aided design (CAD) tool [Betz 97, Luu 09], originally developed by Betz and Rose, supports parameterised island-style FPGA architectures. It can place and route designs and can be used to estimate performance. However, the model of the reconfigurable fabric is obsolete and most commonly available features such as carry-chains cannot be modelled without proper modification to the tool, in which the modification requires significant understanding of the software. In addition, there is no commercial quality synthesis tool to support the VPR tool. This prohibits the use of VPR as it is difficult to implement relatively large circuit defined by users.

Yan and Wilton [Yan 06] employ a synthesisable flow to model reconfigurable fabric. They describe the architectures of the fabric using hardware description language (HDL) and synthesis it with standard cell library design flow. The area and timing information can be obtained directly from the synthesis tool. The model also facilitates rapid evaluation because of the mature ASIC standard cell library design flow. However, it is usually not the most optimum ASIC implementation because of the limitation of the standard cell library design flow. A full-custom ASIC design flow can usually implement the same model with less area and shorter delay. More information regarding to the FPGA modelling is presented in Chapter 3

In terms of high level synthesis on an FPGA device, several schemes such as ASC [Menc 06], Handel-C [Agil 07], Trident [Trip 07], the fly compiler [Ho 02b] are proposed. ASC, also known as a stream compiler, provides a software-like programming interface to hardware design while at the same time keeping the performance of manually-design circuits. It allows existing C/C++ code be seamlessly transformed to ASC code to increase productivity and generate a large selection of implementations. The user can choose the most suitable design from them.

Handel-C is a language that is similar to ANSI-C but dedicated to hardware design. It allows parallel execution constructs and offers a software-influenced hardware design methodology. It can produce a register transfer level netlist based on a code written in C language.

Fly compiler adopts similar semantic to Handel-C. However, the core is simple and lightweight in which new constructs can be easily integrated into the compiler. This

facilitates high level synthesis research and this project employs the fly compiler to produce different experiments efficiently. Furthermore, it is possible to extend the fly compiler such that it can support the proposed FPGA architecture and this is illustrated in Chapter 6.

Studies have been made in optimising floating point operations on existing FPGA architecture. Langhammer [Lang 08] proposes a datapath circuit generator which optimises single precision floating point operations on traditional FPGA devices. The improvements in area and speed are achieved by exploiting fused operations, in which consecutive floating point operations are analysed, redundant normalisations in the operations are removed and a new type of operation is created to replace the original operations.

## 2.4 Floating Point Number System

#### 2.4.1 Overview

Every real number can be approximated by a floating point number in the IEEE 754 standard [ANSI 85] as long as that number is within specific range. The floating point number format is based on scientific notation with limited size for each field. For a normalised floating point number in the IEEE 754 single precision standard where the integer part is always equals to 1, the sign bit is 1 bit in size. The integer part is omitted as it is always equals to 1. The size of fraction part is 23 bit and the size of exponent is 8 bit. The base is always equal to 2 and the total size of a single precision floating point number is 32 bits. In general, an IEEE 754 floating point number *F* can be expressed as follows:

$$F = (-1)^s \times 1.f \times 2^{e-b}, \text{ where}$$

(2.1)

$$b = 2^{e_{size}-1} - 1 \tag{2.2}$$

where *s* stands for the *sign* bit, *f* stands for the *fraction* and *e* stands for the *biased exponent*. In order to express a negative exponent, there is an *exponent bias b* associated with the exponent field. The actual exponent is the value of the exponent field minus the bias. The value of bias depends on the size of exponent  $e_{size}$  as in equation 2.2. The term *significand* represents 1.*f* in which integer field and fraction field are packed together.

For single precision floating point system, the bias is 127 since  $e_{size}$  is 8. If the exponent field *e* is 128, the actual exponent is 128 - 127 = 1. The integer field for most numbers is equal to 1 since they are normalised. Subnormal numbers are indicated by the exponent being 0. In this case,  $F = 0.f \times 2^{-126}$  is represented.

#### 2.4.2 Addition and Subtraction

Let  $F_1$  and  $F_2$  represent the two single precision floating point numbers,  $F_{sum}$  is the sum of these two numbers and  $F_{minus}$  is  $F_1 - F_2$ . As floating point format uses a signed-magnitude representation, the equation  $F_{minus} = F_1 - F_2$  can be rewritten as  $F_{minus} = F_1 + (-F_2)$ . Therefore, this section discusses the addition algorithm only. Subtraction is a variation of addition in which the sign bit of  $F_2$  is inverted.

Let  $F_i$  be denoted as  $(-1)^{s_i} \cdot (1 + 0.f_i) \cdot 2^{e_i - b}$  where  $s_i$ ,  $f_i$  and  $e_i$  are the sign field, fraction field and the exponent field in floating point representation respectively and b is the exponent bias.

The IEEE 754 standard requires that the arithmetic operations, including addition and multiplication should be computed as if first produced an intermediate result correct to infinite precision with unbounded range, and then coerced this to fit in the destination's format. However, it is very expensive in terms of the intermediate storage size, if the operands differ greatly in size. Assuming that size of fraction field is 2,  $1.11 \cdot 2^{10} + 1.00 \cdot 2^{-2}$  would be calculated as

$$x = 1.11000000000 \cdot 2^{10}$$

$$y = 0.0000000001 \cdot 2^{10}$$

$$x + y = 1.11000000001 \cdot 2^{10}$$

which is then rounded to  $1.11 \cdot 2^{10}$ . It uses 13 bits to store the result which is 6 times the size of fraction. When the difference of exponent is larger, the size of intermediate result is larger too.

Without using infinite precision for storing the intermediate result, lengthening the intermediate result by 2 bits at the right is adequate for obtaining properly rounded to zero result. These 2 bits are known as guard bit and round bit respectively. The guard bit can guarantee the relative rounding error in the result is less then  $2\epsilon$ , where  $\epsilon$  is referred to as machine epsilon, the smallest value that can be represented under the given exponent. The round bit can guarantee the rounding to zero mode is always correct [Gold 91]. In general, the sum of  $F_1$  and  $F_2$  is evaluated as shown in Listing 1, where the symbol ## denotes concatenation of two registers,  $s_i$ ,  $e_i$  and  $f_i$  denote the sign field, exponent field and fraction field of the floating point number  $F_1$  and  $F_2$ . However, with some minor modifications, it can be used for arbitrary precision floating point formats. For simplicity, the algorithm does not check any special cases such as negative zero, illegal number and so on. These cases are handled in the hardware implementation of floating point addition.

```

Listing 1: Calculate F_1 + F_2 with floating point arithmetic

Data: F_1 = (s_1, e_1, f_1), F_2 = (s_2, e_2, f_2)

Result: F_{ans} = (s_{ans}, e_{ans}, f_{ans}) = F_1 + F_2

1 e_{diff} \leftarrow e_1 - e_2

2 if e_{diff} \ge 0 then

f_a \Leftarrow f_1

3

f_b \Leftarrow f_2

4

e_s \Leftarrow e_{diff}

5

6 else

7

f_a \Leftarrow f_2

f_b \Leftarrow f_1

8

e_s \Leftarrow 2's complement of e_{diff}

9

10 end

11 if s_a = 1 then

12 | rm_a \leftarrow 2's complement of f_a

13 end

14 if s_b = 1 then

15 rm_b \Leftarrow 2's complement of f_b

16 end

17 f_a \leftarrow (``001'' \# \# f_a)

18 f_b \leftarrow (``001'' \# \# f_b)

19 f_b \Leftarrow \text{shift } f_b \text{ right by } e_{diff} \text{ bits}

20 f_{tmp} \leftarrow rm_a + rm_b

21 if f_{tmp} is negative then

f_{tmp} \Leftarrow 2's complement of f_{tmp}

22

s_{ans} \leftarrow 1

23

24 else

s_{ans} \Leftarrow 0

25

26 end

27 find the leading one of f_{tmp}

28 shift f_{tmp} left until f_{tmp}(msb) = 1,

29 e_{ans} \leftarrow e_a - number of bits shift to left. msb is the location of most significant bit

30 remove the integer bit, f_{ans} = f_{tmp}(msb - 1...0)

31 return s_{ans}, e_{ans} and f_{ans} as sign bit, biased exponent field and fraction field

respectively

```

#### 2.4.3 Multiplication

Multiplication is simpler than addition assuming that a fixed point multiplier is provided. The product of  $F_1$  and  $F_2$ , where both  $F_1$  and  $F_2$  are normalised floating point numbers, is evaluated as in Listing 2. For simplicity, the algorithm does not check any special cases such as negative zero, illegal number and so on. These cases are handled in the hardware implementation of floating point multiplication.

**Listing 2**: Calculate  $F_1 \times F_2$  with floating point arithmetic **Data**:  $F_1 = (s_1, e_1, f_1), F_2 = (s_2, e_2, f_2)$ **Result**:  $F_{ans} = (s_{ans}, e_{ans}, f_{ans}) = F_1 \times F_2$ 1  $s_{ans} \leftarrow s_1 \oplus s_2$ <sup>2</sup> append 1 bit "1" to  $f_1$  and  $f_2$  at left as the hidden integer 3 field 4  $v_1 \Leftarrow "1" \# \# f_1$ 5  $\nu_2 \Leftarrow "1" \# \# f_2$ 6 do fixed point unsigned multiplication  $mc \leftarrow v1 \times v2$ 7  $r_{e1} \leftarrow e_1 + e_2 - b$ s shift mc to left until msb of mc is 1 9  $e_s \leftarrow$  number of bit shifted to left 10  $e_{ans} \leftarrow r_{e1} - e_s$ 11  $f_{ans} \leftarrow mc(44...22)$ 12 **return**  $s_{ans}$ ,  $e_{ans}$  and  $f_{ans}$  as sign bit, biased exponent field and fraction field respectively

### 2.5 FPGA-based Floating Point Units

Table 2.1 presents a list of published information of FPGA-based implementation. Jaenicke and Luk [Jaen 01] have implemented parameterised floating point adder and multiplier on FPGAs. The design is based on Handel-C language and the data format is variance of IEEE 754 standard. It is reported that the floating point adder can perform 28 MFLOPS (million floating operations per second) for arbitrary sizes of fraction and exponent. A 2D Fast Hartley Transform (FHT) processor has been developed by using this FPU as basic building blocks and it can perform a 1K-point transform in 10  $\mu$ s. Belanovic et al [Bela 02] implemented a parameterised floating

| Xilinx<br>Coregen<br>[Xili 05] | Xilinx<br>XC2V1000 | 158MHz      | 176MHz           | 32-bit single<br>precision                    | 5       | yes                       | nearest                                                   | ou                  | no          | 2005 |

|--------------------------------|--------------------|-------------|------------------|-----------------------------------------------|---------|---------------------------|-----------------------------------------------------------|---------------------|-------------|------|

| OpenFPU<br>[Rudo 05]           | Xilinx<br>XC2V1000 | 137MHz      | 142MHz           | 32-bit single<br>precision                    | S       | no                        | zero<br>nearest<br>positive $\infty$<br>negative $\infty$ | yes                 | yes         | 2005 |

| Dido<br>[Dido 02]              | Xilinx VirtexE     | 140MHz      | 140MHz           | 16-bit (6-bit<br>exponent,<br>9-bit fraction) | ഹ       | оп                        | nearest                                                   | оп                  | ou          | 2002 |

| Belanovic<br>[Bela 02]         | Xilinx<br>XCV1000  | I           | I                | 32-bit single<br>precision                    | n       | yes                       | zero<br>nearest                                           | yes                 | yes         | 2002 |

| Jaenicke<br>[Jaen 01]          | Xilinx<br>XCV1000  | 28MHz       | 28MHz            | 32-bit single<br>precision                    | ъ       | yes                       | nearest                                                   | yes                 | no          | 2001 |

|                                | Target device      | Adder speed | Multiplier speed | Data format                                   | Latency | Parameterised<br>bitwidth | Rounding mode                                             | Subnormal<br>number | Open source | Year |

Table 2.1: FPGA-based floating point operators implementations.

point library for use with reconfigurable hardware. It is based on the IEEE 754 floating point format standard. The library includes addition, subtraction, multiplication and conversion between fixed point and floating point numbers. All of these modules are specified in VHDL and implemented on the Wildstar reconfigurable computing engine. They are fully-pipelined and cascadable to form pipelines of floating point operations. This library is used to develop a hybrid implementation of the K-means clustering algorithm applied to multi-spectral images.

Dido et al. [Dido 02] proposed a flexible floating point format which is optimised for video signal processing application. The format employs moderate bitwidth but it can maintain sufficient output accuracy. This can deliver better performance and consume less area with acceptable trade-off on accuracy.

To allow comparison between traditional FPGA device and proposed reconfigurable devices, floating point operators which support arbitrary precision and floating point benchmark circuits have been developed in HDL model and implemented on commercial FPGA devices. The floating point operators are fully compliant with IEEE 754 [ANSI 85] standard and support 4 rounding modes, subnormal numbers and exceptions. In addition, they are fully-pipelined and arbitrary size of exponent and fraction are allowed by modifying the model slightly. To support parameterised floating point operators, a HDL generator is developed using the Perl language which can generate the associated logic for a specific size of exponent and significant on-the-fly.

**Floating Point Adder** – The floating point adder is based on a heavily modified opensource floating point unit [Rudo 05]. It consists of several blocks, namely, a prenormalisation block, an addition block, a post-normalisation blocks and an exception handling block. The datapath of the floating point adder is shown in Figure 2.2. The figure captures essential steps in computing floating point addition as shown in the Listing 1. In the pre-normalisation stage, the inputs are registered and the exponents are compared. The inputs are swapped if the exponent of first operand is smaller than the second operand. The fractions are shifted to right accordingly and operation mode

Figure 2.2: Datapath of floating point adder.

Figure 2.3: Datapath of floating point multiplier.

which indicates if the effective operation (either addition or subtraction) is evaluated. The most expensive circuit for the pre-normalisation stage is the barrel shifter.

Special number from the input such as subnormal number, infinity and not a number (NaN) are handled in the exception handling block. Corresponding flags, such as subnormal flag, zero flag, infinity flag, NaN flag are set according to the combination of the input. This circuit is simple and only comparators are required. The addition block takes the output from the pre-normalisation block, in which the data has been properly aligned and the operation mode is well defined. The addition block adds or subtracts the numbers according to the operation mode.

The post-normalisation block is the most complicated circuit in the floating point adder. After the intermediate result is generated by addition block, a priority encoder inside the post-normalisation block takes the result as an input and counts the number of leading zero of the result. The exponent is then adjusted and the fraction is shifted to left depending on the number of leading zero. Different rounding scheme is enforced according to the input to produce final result. Exception flags like inexact number, overflow, underflow is generated based on the final result. All the outputs are registered so the result and the corresponding exception flags are given in next clock cycle. This block contains two expensive circuits, namely barrel shifters and a priority encoder.

**Floating Point Multiplier** – Figure 2.3 illustrates the datapath of floating point multiplier. Same as the floating point adder, the floating point multiplier is based on the same open-source floating point unit, and it has been heavily modified. It consists of several blocks, namely, a pre-normalisation block, a multiplication block, a postnormalisation block and an exception handling block. In the pre-normalisation stage, the intermediate exponent is determined by adding exponents from the inputs. Hidden bits of the fractions are recovered based on the exponent values. This block does not have expensive circuits and most of them are comparators and adders.

The exception block of floating point multiplier is the same as the one in floating

point adder. It detects any special input values. The multiplication block takes the output from the pre-normalisation block, in which the hidden bits in fraction has been recovered properly and an integer multiplication is computed by a multiplier. The results are then populated to post-normalisation block. The multiplier circuit consumes significant amount of resource in this block.

The post-normalisation takes the intermediate product from the multiplication block as input. A priority encoder in the post-normalisation block counts the number leading zero in the intermediate product. Similar to the post-normalisation block in the floating point adder, the exponent is then adjusted and the fraction is shift to the left based on the number of leading zero. Different rounding mode is enforced according to the input to produce final result. Exception flags like inexact number, overflow, underflow is generated based on the final result. And all the outputs are registered and the final result and the associated flags are given in next clock cycle. This block contains two expensive blocks, namely barrel shifters and a priority encoder.

**Verification** – To verify the correctness of the floating point operators so that they are compliant with the IEEE 754 standard, an open-source program called *TestFloat-2a* [Haus 98] is employed. By slightly modifying the output options in *TestFloat-2a* program, it can create a large number of test cases, which make up of simple pattern tests intermixed with weighted random inputs for the floating point operators. The "level 1" test in *TestFloat-2a* covers all 4 rounding modes, and all boundary cases of given arithmetic, including underflows, overflows, invalid operations, subnormal inputs, zeros (positive and negative), infinities (positive and negative), and NaNs. Each test case contains an operation, a rounding mode, floating point numbers to be evaluated, an expected result and expected exception flags. The expected results and the expected exception flags are computed purely in software and do not rely on machine-specific floating point implementations. A corresponding testbench written in Verilog is created which reads the test cases generated by *TestFloat-2a*, invokes the corresponding floating point operator to compute the result, and compares the result and the exception flags with the expected output. The test case is created with switch

| Floating Point Operation            | Number of tests |

|-------------------------------------|-----------------|

| Floating Point Addition/Subtraction | 371712          |

| Floating Point Multiplication       | 371712          |

OperatorSlicesEmbedded MultiplierLatencyFrequency (MHz)fpadd2177705134fpmul221509576

Table 2.2: Number of tests generated by TestFloat-2a.

Table 2.3: FPGA implementation results for double precision floating point operators.

"level 1" in the initial settings of *TestFloat-2a*. Table 2.2 shows the number of test vectors has been created for specific floating point operation. All test cases assume double precision floating point format. The testbench is run in ModelSim 5.7d and no errors are found.

**Implementation** – In order to compare with the floating point core using current commercial FPGA with the one using *customisable* FPGA, the floating point operator circuits have been implemented on FPGA device. The reference FPGA device is XC2V6000 and the speed grade is -5. All the design is synthesised using Synplify Premier 9.0. The designs are placed and routed and the area and the timing are obtained by vendor CAD suites ISE 9.2i. Table 2.3 presents the area and frequency of the double precision floating point adder and multiplier.

# 2.6 Floating Point Applications

Many floating point systems have been implemented on FPGA devices. In [Ho 03], an N-body solver is developed using Virtex-E device. The computations are based on parameterised floating point library and can achieve a peak speed of 3GFLOPS. In [Unde 04], three of the basic linear algebra subroutine (BLAS) functions are estimated and it suggests that FPGA-based implementations outperform modern generalpurpose processor on double precision floating point operations. It also mentions that unlike CPUs, FPGAs are usually limited by peak FLOPS rather than by memory bandwidth so improving the floating point computation performance of an FPGA can obtain similar gain on overall systems.

Zhang et al. [Zhan 05] employ floating point arithmetic to compute the Brace, Gatarek and Musiela interest rate model for pricing derivatives. While running at relatively low frequency (50MHz), the performance is 25 times faster than software running on a 1.5GHz Intel Pentium 4 machine.

Callanan et al. [Call 06] demonstrate an FPGA based lattice QCD processors using IEEE double precision floating point format and compared with corresponding ASIC based solutions and PC cluster-based solutions. The FPGAs version, which is implemented on a Virtex II FPGA device, can achieve 1.2GFLOPS when performing Dirac operation and deliver 0.94GFLOPS on conjugate gradient solver. The performance of Dirac operation is two times better than purely software implementation.

Zhuo and Prasanna [Zhuo 04] propose an FPGA-based architecture for floating point matrix multiplication. It employs a linear array architecture and effectively utilises the hardware resources on the entire FPGA device while reduces the routing complexity. Their work achieves comparable floating point computation performance and can deliver up to 26.6GFLOPS and 12.3GFLOPS for single precision and double precision floating point format respectively.

Morris and Prasanna [Morr 05] report an FPGA-based floating point Jacobi iterative solver. The design employs a deeply pipelined, highly parallelised IEEE double precision floating point operator. The solver is implemented on a Virtex II Pro device running at 77MHz. Depending on the nature of input data, it can achieve up to 36.8 times speedup when compared with a single processor implementation.

# 2.7 Benchmark Circuits

As there are no existing standard benchmark circuits for floating point applications, a set of benchmark circuit is implemented using the fly compiler [Ho 02b] or using HDL. Significant amount of time in developing the benchmark circuits are reduced as the fly compiler can generate a circuit which contains a datapath and associated control signals from a software description.

In addition, all the floating point application benchmark circuits assume double precision floating point arithmetic and employ round-to-nearest-even rounding mode, while the exception signals from the floating point operator are ignored in the circuits. By describing the application using Perl-like description and simulate it in Perl environment, the fly compiler can speed up the implementation time of the benchmark applications. Four application circuits have been generated using the fly compiler, which include a digital sine cosine generator (*dscg*), an ordinary differential equation solver (*ode*), a 3-by-3 matrix multiplication (*mm3*), a four-tap finite impulse response filter (fir4), a butterfly circuit for fast Fourier transform (*bfly*) and a financial derivatives modelling circuit using Brace, Gątarek and Musiela model (*bgm*) [Zhan 05]. These benchmark applications contain different number of floating point operators the inter-connection between those floating point operators are different. The benchmark applications further assume the input data comes from an off-chip memory.

## 2.7.1 Digital Sine-Cosine Generator (dscg)

Digital sine-cosine generator [Mitr 98] has a number of applications, such as the computation of discrete Fourier transform and in certain digital communication systems, such as in future Hiperlan systems for high performance wireless indoor communication. Let  $s1_n$  and  $s2_n$  denote the two outputs of a digital sine-cosine generator, the outputs at the next sample can be computed using the following formula:

$$\begin{bmatrix} s1_{n+1} \\ s2_{n+1} \end{bmatrix} = \begin{bmatrix} \cos(\theta) & \cos(\theta) + 1 \\ \cos(\theta) - 1 & \cos(\theta) \end{bmatrix} \begin{bmatrix} s1_n \\ s2_n \end{bmatrix}$$

(2.3)

# 2.7.2 Ordinary Differential Equation (ode)

Many scientific problems involve the solution of ordinary differential equations. An ODE solver (ode) is implemented as part of the floating point benchmarks. The benchmark circuit solves the ODE [Math 99]:

$$\frac{dy}{dt} = \frac{(t-y)}{2} \text{ over } t \in [0,3] \text{ with } y(0) = 1$$

(2.4)

Euler method is used and y is approximated by

$$y_{k+1} = y_k + h \frac{(t_k - y_k)}{2}$$

and  $t_{k+1} = t_k + h$  (2.5)

where *h* is the step size, the smaller value of *h*, the more accurate of the result.

The ordinary equation solver can take the step size h as the parameter and return the value of y.

# 2.7.3 Matrix Multiplication (mm3)

Matrix multiplication is used frequently in different domains. Hence a 3x3 matrix multiplication application benchmark circuit is developed. The core of the circuit implements the operation required to evaluate an element of the resulting matrix, which is a vector dot-product. Extra logic is added to control the dataflow of the circuit.

Figure 2.4: Four-tap FIR filter.

## 2.7.4 FIR Filter (*fir4*)

Digital filter is one of the most common applications which requires floating point arithmetic for high accuracy and precision, we have implemented a 4-tap finite impulse response filter, which is characterised by the following equation:

$$y_4 = \sum_{j=0}^4 k_j x_{4-j} \tag{2.6}$$

where  $x_i$  is the input of the filter,  $k_i$  is the filter window and  $y_i$  is the output. The datapath of the filter is shown in Figure 2.4.

# 2.7.5 Butterfly Circuit (bfly)

The fast Fourier transform (FFT) is another important signal processing primitive. The FFT is composed from butterfly operations which compute  $z = y + x \times w$ , where x and y are the inputs from previous stage and w is a twiddle factor. All values are complex numbers; therefore each multiplication involves 4 multipliers and 2 adders (bfly). A state machine is implemented to control the dataflow of the circuits. Figure 2.5 illustrates the datapath of a single butterfly which is used as the benchmark circuit.

Figure 2.5: One butterfly stage in FFT.

## 2.7.6 Brace, Gątarek and Musiela (bgm)

The datapath of a design to compute Monte Carlo simulations of interest rate model derivatives priced under the Brace, Gątarek and Musiela (BGM) model is used as the final test circuit (*bgm*) [Zhan 05]. Denote  $F(t, t_n, t_{n+1})$  as the forward interest rate observed at time *t* for a period starting at  $t_n$  and ending at  $t_{n+1}$ . Suppose the time line is segmented by the reset dates  $(T_1, T_2, ..., T_N)$  (called the standard reset dates) of actively trading caps on which the BGM model is calibrated. In the model, the forward rates { $F(t, T_n, T_{n+1})$ } are assumed to evolve according to a log-normal distribution. Writing  $F_n(t)$  as the shorthand for  $F(t, T_n, T_{n+1})$ , the evolution follows the stochastic differential equation (SDE) with *d* stochastic factors:

$$\frac{dF_n(t)}{F_n(t)} = \vec{\mu_n}(t)dt + \vec{\sigma}_n(t) \cdot d\vec{W}(t) \qquad n = 1 \dots N.$$

(2.7)

In this equation,  $dF_n$  is the change in the forward rate,  $F_n$ , in the time interval dt. The drift coefficient,  $\vec{\mu_n}$ , is given by

$$\mu_{n}(t) = \vec{\sigma}_{n}(t) \cdot \sum_{i=m(t)}^{n} \frac{\tau_{i}F_{i}(t)\vec{\sigma}_{i}(t)}{1 + \tau_{i}F_{i}(t)}$$

(2.8)

where m(t) is the index for the next reset date at time t and  $t \leq t_{m(t)}$ ,  $\tau_i = T_{i+1} - T_i$ and  $\sigma_n$  is the d-dimensional volatility vector. In the stochastic term (the second term on the right hand side of Equation 2.7),  $d\vec{W}$  is the differential of a d-dimensional uncorrelated Brownian motion  $\vec{W}$ , and each component can be written as  $dW_k(t) = \epsilon_k \sqrt{dt}$  where  $\epsilon_k$  is a Gaussian random number drawn from a standardised normal distribution, i.e.  $\epsilon \sim \phi(0, 1.0)$ .

# 2.8 Terminology

Here is a list of special terminologies and the corresponding abbreviations used throughout the thesis.

- Field programmable gate array (FPGA).

- Application specific integrated circuit (ASIC).

- Floating point unit (FPU).

- Very high speed integrated circuits hardware description language (VHDL).

- Logic cell (LC) It describes the smallest logic unit in the FPGA. This consists a 4-input LUT, register and dedicated carry logic.

- Logic block (LB) It refers to an array of LCs which are interconnected via the local routing resources in the FPGA.

- Embedded block (EB) It refers to heterogeneous element in the island-style FPGA. An EB usually contains specific function in an FPGA such as embedded multiplier and block memory.

- Virtual embedded block (VEB) It refers to virtual heterogeneous element in the island-style FPGA. VEB can model arbitrary embedded block even if such block does not exist in real FPGA devices. More detail on VEB is given in Chapter 3.

- Fine-grained unit (FGU) It refers to homogeneous element in the island-style FPGA. It is usually the same as LC unless otherwise specified. We use the term embedded block.

- Coarse-grained unit (CGU) In later context of the thesis, we use the term CGU to describe a family of heterogeneous architecture proposed in this thesis. It can be considered as a subset of EB.

- Standard FPGA It refers to commodity FPGA devices which are usually commercially available.

- Register transfer language (RTL).

# 2.9 Summary

This chapter introduces the work related to the project. Section 2.2 describes the common island-style fine-grained fabric and the application-specific heterogeneous fabric. Section 2.3 discusses the CAD tools for modelling an FPGA and the high level synthesis design tools for implementing user circuits on an FPGA. Floating point number system, including the number representation and primitive operations is covered in Section 2.4. Some published information of FPGA-based floating point units and the architecture of our FPGA-based floating point operators are summarised in Section 2.5. Section 2.6 introduces some floating point applications implemented on FPGA devices and their performance. Section 2.7 compiles a set of floating point benchmark circuits which are used iteratively in the thesis. Finally, Section 2.8 lists terminologies used in the thesis.

# **Chapter 3**

# Virtual Embedded Block

# 3.1 Introduction

Similar to designing ASIC circuitry, when designing FPGA architecture, one major concern is to identify a justified model which can estimate the performance in terms of area, delay and power consumption based on user-supplied applications.

Modelling ASIC circuitry is relatively simple once the netlist of the circuit is defined. Given a set of process parameters, the area of a circuit can be estimated by counting the number of transistors used with some assumptions on the routing. The timing or critical delay can be estimated by enumerating the delay of each combinational path.

Modelling reconfigurable architecture is a non-trivial process. The major difference between ASIC and reconfigurable devices is the latter one can change their datapath substantially after fabrication. Because of this fundamental difference, definitions of "area" and "delay" are not the same as those in ASIC. Area is not simply the transistor count of the device and delay is not the critical path of the device. Rather, we wish to adopt a definition of area and delay to reflect characteristics of applications implemented on the device.

An application implemented on an FPGA device does not consume all the reconfig-

urable resources on the FPGA. Only part of reconfigurable resources are used to perform required operations. Therefore, area is tied to the transistor count of the configured region in the device while delay is the critical path of the configured region in the device. When enumerating the delay of each path, the model has the ability to recognise the delay of each fine-grained, coarse-grained components and interconnect along the paths. It also adds complexity in modelling FPGA device.

FPGA vendors offer design tools for users to model and implement applications on their FPGAs. The tools often involve a tool which translates user applications described in HDL to an architecture-specific netlist. This process usually refers to synthesis. The netlist is then implemented in a reconfigurable device. The implementation process defines the configured region in the device. Area and timing can be retrieved according to the implementation results. The tools released by vendors support their own devices. In other words, the tools support different applications but are limited to specific devices.

In this research, we begin with modifying existing FPGA architecture by embedding user-defined heterogeneous blocks to reconfigurable device to accelerate floating point computations. We show that this approach allows us to reuse existing design tools to model new FPGA architecture and also allows us to compare the new FPGA architecture with the existing device.

To capture the performance of new FPGA architecture, we employ floating point applications as benchmarks. It is because we need to deal with more advanced architectures with different heterogeneous blocks which have multiple granularities. In addition, our application domains usually involve floating point arithmetic so we can select representative kernels or applications to further optimise the architectures. In order to establish a model for reconfigurable architecture for floating point computation, the following issues have to be considered:

1. The model can capture the performance by providing the area, delay and power data associated with the benchmark circuit.

- 2. The data obtained in 1 are comparable to existing FPGA devices.

- 3. The model can allow the reuse of existing CAD tools, such as synthesis tools, place and route tools, and mapping tools as much as possible.